共振型ゲート駆動回路の電力低減とゲート電流制御に関する研究

■省電力効果

節電の効果としては,本ゲート駆動回路はチョッパー回路を構成していますのでインダクタによるフリーホイールダイオードを介しての還流によってエネルギー効率良く伝達されます.ご存知だと思いますが,たとえばゲート充電の過程では,SW1オン時に電源B1からIGBTゲートに対しインダクタLgを介し充電を行いつつインダクタLgに磁気としてエネルギーを蓄える状態となって,つづいてSW1をオフ時には,先ほどのインダクタLgに蓄えられたエネルギーがSW2に寄生する(フリーホイール)ダイオードを介して通電することでIGBTゲートに充電されます.

ゲート放電の過程では,SW2オン時にIGBTゲートからインダクタLgを介して放電を行いつつインダクタLgに磁気としてエネルギーを蓄える状態となって,つづいてSW2をオフ時には,先ほどのインダクタLgに蓄えられたエネルギーがSW1に寄生する(フリーホイール)ダイオードを介して通電することで電源B1に電力が回生されます.

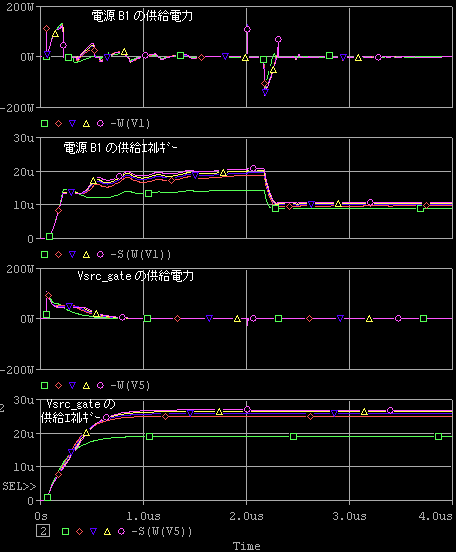

図a-9 駆動電力比較

□0V

◇100V

▽200V

△300V

○400V

ここで具体的なIGBTの1回のスイッチングの過程でのゲート駆動時の電力について,ゲート抵抗モデルと本ゲート駆動回路モデルとをそれぞれ算出した結果を図a-9に示しています.IGBTの駆動条件については図a-7,図a-9に示す各部波形のシミュレーションと同期しています.

図a-9中の”電源B1の供給電力”については,プラス側が電力供給でマイナス側が電力回生を示しています.IGBTゲート充電時には電源B1より電力を供給し,ゲート放電時にはゲート容量に蓄えられているエネルギーが電源B1に回生されている様子がわかると思います.これに対し従来のゲート抵抗による供給電力はゲート充電時に電力を供給のみで回生されません.

ここで,IGBTの1スイッチングの過程(オフ状態→オン状態→オフ状態)におけるゲート駆動エネルギーの収支について算出したものが図a-9中の”電源B1の供給エネルギー”と”Vsrc_gateの供給エネルギー”です.これらは電源B1供給電力およびVsrc_gate供給電力の時間積分によって求められる累積された電力すなわちIGBT 1スイッチング当たりの供給エネルギーとなります.これを検証することで各ゲート駆動回路の消費電力を比較することができます.そこで,それぞれのIGBT 1スイッチング当たりの供給エネルギーは

本ゲート駆動回路:11[μJ]

ゲート抵抗による:28[μJ]

とおよそ従来ゲート抵抗方式の40%弱の消費電力でゲート駆動できることが算出されました.よってこのシミュレーション条件においては電源B1の電力定格は従来のゲート抵抗モデルの半分以下で実現可能となります.この技術によって電源B1の小型化とさらにゲート駆動回路の発熱低減による高密度化を可能にします.

以降蛇足ですが,この損失シミュレーションでの実効損失を対象としている部品は,本ゲート駆動回路ではSW1,SW2のMOS-FET,ゲート抵抗モデルではゲート抵抗Rgと,さらにCM600HA-12です.本ゲート駆動回路の損失シミュレーションにおいてはとくに,SW1,SW2のMOS-FETの損失が評価において重要と考えています.仮にこのSW1,SW2の損失が大きい場合,本ゲート駆動回路の省電力効果を相殺してしまう可能性もあるからです.このシミュレーションにおいては現実的に入手の容易なMOS-FETの仕様を想定しています.そのSW1,SW2のMOS-FETの一般仕様は

ID=10A〜30A

VDS=100V〜500V

RDS=〜0.33Ω

tr=〜40ns

また,シミュレーションに使用したMOS-FETのSPICEモデルは次の通りです.

.MODEL FET NMOS(

+ LEVEL=3

+ L=2.0000E-6

+ W=20

+ KP=1.0452E-6

+ RS=10.000E-3

+ RD=.32659

+ VTO=2.8000

+ RDS=10.000E6

+ TOX=2.0000E-6

+ CGSO=175.93E-12

+ CGDO=1.6264E-12

+ CBD=2.4802E-9

+ MJ=1.1551

+ PB=2.4390

+ RG=10.000E-3

+ IS=1.0252E-6

+ N=2.0380

+ RB=1.0000E-9

+ GAMMA=0

+ KAPPA=0)

一般のゲート抵抗方式ではIGBTの立ち上がり時間(tr)の設定をゲート抵抗によって調整します.本ゲート駆動回路でのtr設定は,ゲート抵抗モデルにおけるRg=2[Ω]相当に設計しております.この回路によって,trを変更する場合,ゲート抵抗方式のように容易に変更できません.SW1,2のスイッチング周波数,デューティ,Lgなどオーバーシュートに絡む多くのパラメータを調整する必要があります.

IGBTの立ち上がり時間(tr)の高速化にあたっては低Lg化,SW1,2スイッチング周波数の高周波化が要求されますが,これにともなってMOS-FETの損失の増加が課題となります.一般にMOS-FETの高速化を求める場合,低tr化に反してRDSの高抵抗化の相反する特性をもつため,単純にスイッチング損失,リカバリー損失の増加だけでなく同時にジュール損失の増加も課題となります.こういったMOS-FET選定の要素も含めて本ゲート駆動回路を設計いただくことが実務上重要なポイントになります.