エミッタ容量(Cib)とスイッチング遅延

トランジスタにはコレクタ−ベース間,ベース−エミッタ間にPN構成上,それぞれコレクタ容量(Cob),エミッタ容量(Cib)の静電容量が寄生することを説明しました(詳細こちら).これら容量の存在によって,トランジスタの動作に与える影響を考えます.

ここでは,トランジスタのスイッチング機能とエミッタ容量Cibとの関係について求めます.

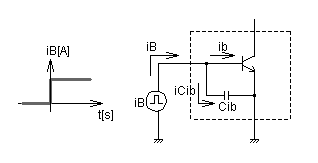

図3-3-16 Cib分離の簡易モデルとシミュレーション系

図3-3-16は,NPNトランジスタのエミッタ容量とスイッチングの特徴についてのシミュレーション系で,ベース,エミッタ間に電流源iBを接続してステップ状の定電流を与えます.点線で囲んでいる部分を通常使用する一体の(寄生容量を含む)トランジスタとして想定します.

点線内部ではトランジスタに寄生するエミッタ容量(Cib)を図のように分離して示すことにします.点線内中心に示すトランジスタは次の式3-3-4の関係のみ機能(電流増幅)を持つ簡易的なモデルとしてここでは考えることにします.

| ic=hFE ib | 式3-3-4 | ib:ベース電流[A] ic:コレクタ電流[A] hFE:直流電流増幅率[倍] |

まず最初にエミッタ容量のみの影響について考えます.ここでは,コレクタ端を開放として考え,Cob等コレクタ側の影響を排除してCibとibの関係を求めていきます.(ただし,コレクタ端に直流電源が接続されるなど,コレクタが交流的に接地される場合には,CibにCobが並列接続されている状態と同様に考えることもできます.)

まず,ベース−エミッタ間電圧とibの関係について.この関係はPNダイオードのVF−IFの関係(次の式3-2-5)と同様に考えることができます(詳細はこちら).

| IF =IS(AbVF-1) | 式3-2-5 | VF[V]:順方向バイアス IS[A]:飽和逆方向電流 A[ ]:固定定数 b[V-1]:温度に係わる係数 |

つづいて電流源iBと各パラメータの関係は

|

式3-3-5 |

これら式3-3-5の関係をグラフに示すと

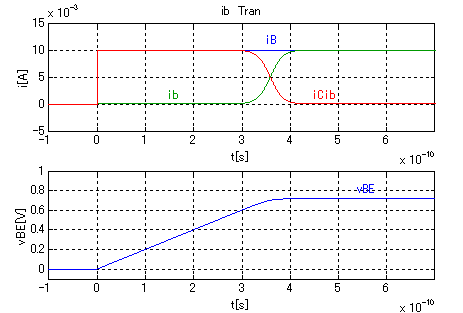

図3-3-17 ベース電流とエミッタ容量電流の関係 シミュレーション

図3-3-17では,t=0[s]のときvBE=0[V]と電圧が与えられていない条件で,iBにステップ状の電流を与えた際の,ibおよびiCibの電流を計算しています.式3-2-5のibのvBEに対する指数関数の関係からもわかるように,vBEが小さい条件(iBステップ電流印可直後)ではibは流れにくく,iB電流の多くはCibに充電電流として流れることになります.

時間経過とともに,Cibが充電されvBEの増加にともなってib電流が指数関数的に急激に増加を始めて,ibがiBに漸近していきます.

もうちょっと簡単に考えれば,vBEがPNの障壁電位に近づくとibが流れ出すことからも,Cibの存在によってvBEバイアス印可のためのCibの充電時間(遅延)が設定されることになります.図3-3-17の波形からも3×10-10〜4×10-10[s]のiBに対するibの遅延が容易に読みとれると思います.

この遅延時間は,Cibの充電に要す時間すなわち

| |

式3-3-6 | TCib[s]:Cibによる遅延時間 ΔVBE[V]:vBEバイアス Cib[F]:エミッタ容量 iB[A]:ベース電流 |

Cib 容量値に比例し,iBベース電流値に反比例します.

ただし,リニア領域で使用する場合デジタル用途に比べ,ΔvBEの電圧変動幅が小さくなるため遅延時間ΔTCibは小さいものとなります.